miniHIL Motivation

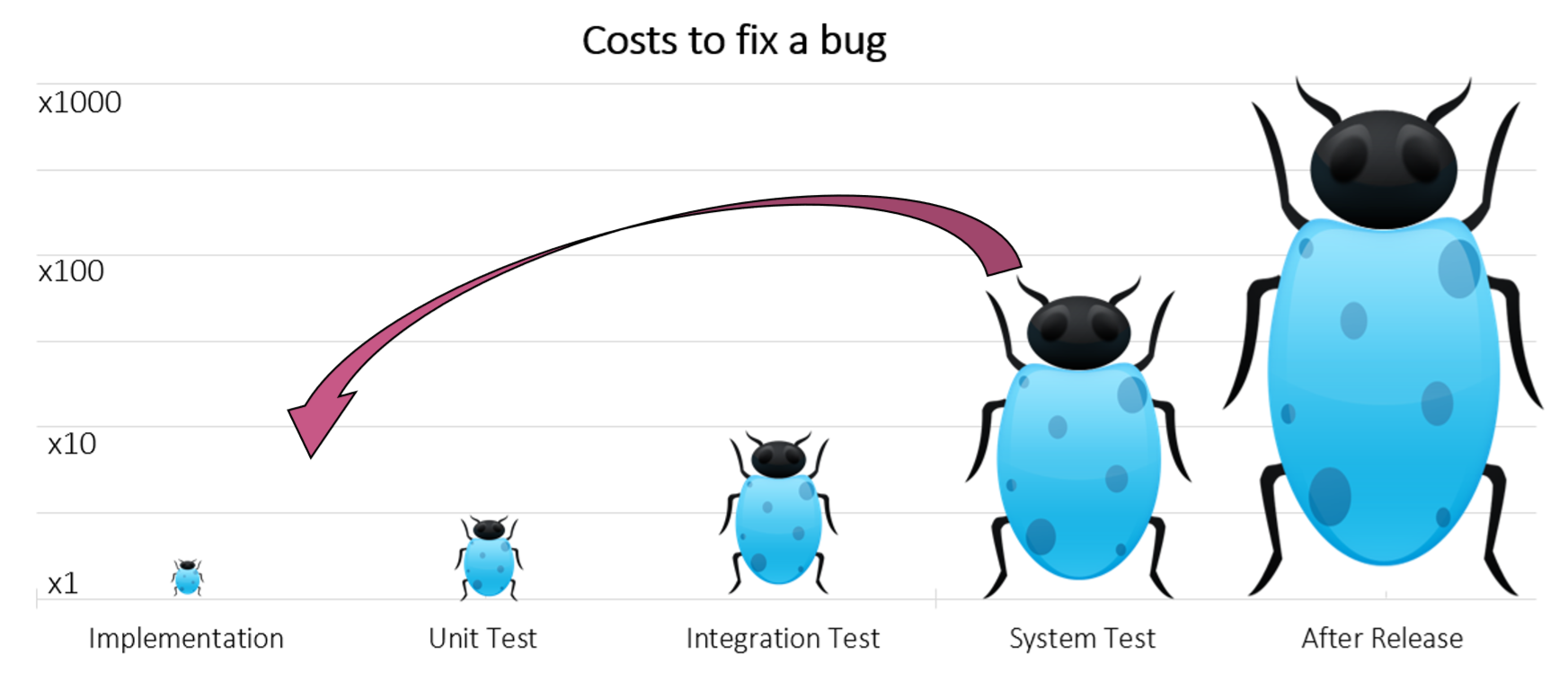

Well designed and reliable embedded systems are built on a foundation of rigorous and thorough testing throughout all stages of its development. This is particularly important in its early stages, as errors/bugs become increasingly more expensive to fix as the project progresses. For example, fixing a bug found during the implementation stage could be a matter of changing a few lines of code, however, fixing a bug found after release could require a product recall costing millions of dollars!

The problem that embedded developers face is that the high complexity of modern embedded systems makes it very difficult to perform any meaningful tests in a purely software environment. Unlike software systems, embedded systems interact with physical interfaces and real-time inputs and outputs, both of which aren’t emulated well in pure software tools.

Hardware in the Loop (HIL) tests provide a means of testing an embedded system using real signals. As it stands, the existing hardware platforms and software tools for HIL tests are often too expensive to use at every workstation during development. As well as this, the development of system HIL tests requires a vastly different skill set to the development of the system under test (SUT), so the testing stage is commonly put off until far later in the system’s development.

Hardware in the Loop for Everybody

The PROTOS miniHIL’s purpose is to provide the tools necessary to perform HIL tests directly to developers, so that comprehensive testing can be performed at all stages of development. This opens up a platform to eliminate bugs early and prevent them from becoming very expensive mistakes!

The PROTOS miniHIL board interfaces a Device Under Test (DUT) with the test system as well as providing a human machine interface (HMI) for the developer. The HilSimGUI allows developers to monitor exactly what’s happening on their system-under-test in real time. Combined with the PROTOS CaGe framework, these tools allow developers to take full control of their system’s testing stage.